US007038552B2

# (12) United States Patent Brett et al.

## (10) Patent No.: US 7,038,552 B2

### (45) **Date of Patent:**

May 2, 2006

# (54) VOLTAGE CONTROLLED OSCILLATOR HAVING IMPROVED PHASE NOISE

(75) Inventors: **Stephen Jonathan Brett**, Hailsham

(GB); Jonathan Richard Strange, Reigate (GB); Paul Fowers, Tonbridge (GB); Christopher Geraint Jones,

Maidstone (GB)

(73) Assignee: Analog Devices, Inc., Norwood, MA

(US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 77 days.

(21) Appl. No.: 10/679,997

(22) Filed: Oct. 7, 2003

(65) Prior Publication Data

US 2005/0073371 A1 Apr. 7, 2005

(51) Int. Cl.

H03L 5/00 (2006.01)

H03L 7/099 (2006.01)

H03B 5/00 (2006.01)

H03B 5/12 (2006.01)

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 6,483,391<br>6,680,655<br>2003/0001684 | B1* | 1/2004 | Magoon et al           |

|----------------------------------------|-----|--------|------------------------|

| 2003/0025566                           |     | 2/2003 | Rogers                 |

| 2003/0171106                           |     | 9/2003 | Dunworth et al 455/262 |

### FOREIGN PATENT DOCUMENTS

EP 1333574 8/2003

#### OTHER PUBLICATIONS

PCT/US2004/032274 International Search Report Apr. 26, 2005.

\* cited by examiner

Primary Examiner—David Mis (74) Attorney, Agent, or Firm—Wolf, Greenfield & Sacks, P.C.

#### (57) ABSTRACT

A frequency agile voltage controlled oscillator is provided in which amplitude control is performed by digitally controlling the current supplied to the oscillator from a current source (10). The use of digital control means that phase noise performance of the oscillator is not degraded by the introduction of noise from the current source controller.

#### 28 Claims, 13 Drawing Sheets

Fig. 1

Fig. 2

Fig. 3

Fig. 4

Fig. 9

## VOLTAGE CONTROLLED OSCILLATOR HAVING IMPROVED PHASE NOISE

The present invention relates to a voltage controlled oscillator having reduced phase noise, and to an apparatus 5 for and method of controlling such an oscillator.

#### BACKGROUND OF THE INVENTION

Mobile telephones, in common with many radio systems <sup>10</sup> up-convert a signal to be transmitted from a base band to the transmission frequency. A relatively wide spread of transmission frequencies are supported by the mobile telephone and consequently the transmission oscillator and local oscillator provided within such a telephone need to be tuneable <sup>15</sup> over a relatively wide range of frequencies.

In general, if it is desired to tune a voltage controlled oscillator, VCO, over a relatively wide frequency range, then a relatively large constant of proportionality  $K_{VCO}$  between the oscillator output frequency and the oscillator input control voltage is required. The use of a large  $K_{VCO}$  enables the tuning range to be traversed quickly. This means that the local oscillator can be rapidly moved between frequencies and locked to the new frequency. There is, however, a penalty to be paid for this ease of tuning. Any noise appearing on the control voltage has potential to appear in the oscillator's output spectrum. This noise can result in fluctuations of the phase of the oscillator's output from the phase of an ideal sinusoid having the same frequency as the nominal frequency of the oscillator. These deviations amount to phase noise at the output of the oscillator.

The GSM standard for mobile telephones places limits on the phase noise that can be permitted in the transmission envelope of a mobile telephone. The limits are mandatory in that devices falling outside of these limits will not be accredited for use. The production of phase noise in the local oscillator or the transmission oscillator of the mobile telephone could easily cause the output signal's power density away from the nominal transmit frequency to exceed the permitted transmission power envelope. As a result, the voltage controlled oscillators of a mobile phone have typically been expensive discreet devices.

One way to address the phase noise problem is to have the voltage controlled oscillator with a much lower  $K_{VCO}$ . Thus any noise on the oscillator control voltage has a proportionally reduced effect on the oscillator output frequency. However this, whilst reducing phase noise, makes it more difficult to tune the oscillator over a wide operating range.

Within a mobile telephone the VCO is included within a phase locked loop (PLL). Phase locked loops are well known to a person skilled in the art. A reference signal and a signal derived from the output of the VCO are compared by a phase detector. The output of the phase detector is then transformed (typically by low pass filtering) into a control signal for the VCO.

For some oscillator topologies variations in oscillator amplitude give rise to variations in oscillator frequency and also affect  $K_{\nu CO}$  and hence the loop gain of the PLL. This can make the design and control of a fast response frequency agile low phase noise VCO and associated circuitry difficult.

However, for other reasons the designer may actually wish the oscillator amplitude to be set to different target values for different modes of operation of the telephone. Thus oscillator amplitude may be larger during a transmit 65 period compared to a receive period as phase noise requirement in the transmit process are more stringent.

2

#### SUMMARY OF THE INVENTION

According to the first aspect of the present invention there is provided a variable frequency oscillator comprising: a variable frequency oscillator core; an oscillator controller; and an output voltage stabilisation device for maintaining an amplitude of an oscillator output within a predetermined range, wherein the variable frequency oscillator core is controllable to operate in one of a plurality of frequency bands and has a frequency control input responsive to the oscillator controller, and where in order to set a new operating frequency the oscillator controller performs a frequency search through the bands to identify an appropriate band and wherein amplitude stabilisation is performed during band selection.

It is thus possible to provide improved stability in both the amplitude and frequency domains of the oscillator. This is important since amplitude and frequency control are not completely independent of one another and hence adjusting one of these parameters of oscillator performance has an effect on the other parameter.

Preferably the variable frequency oscillator is a voltage controlled oscillator.

Preferably the task of tuning the oscillator towards a target frequency is performed in an iterative manner. Thus the oscillator frequency converges on the target frequency. Such frequency control can be performed over a plurality of tuning steps. Preferably amplitude stabilisation is performed in association with at least one of the tuning steps. If the tuning is performed using a successive approximation approach to locating the correct frequency then the amplitude stabilisation may be performed in respect of all of the approximation steps, or only some of the approximation steps, for example the most significant bits/steps.

In an embodiment where binary weighted tuning capacitors are switched in and out of an inductor-capacitor resonant circuit of the oscillator, the switching in of a capacitor causes the resonant frequency to drop. Similarly removal of a capacitor from the resonant circuit causes the resonant frequency to rise. Thus, following the instruction to select a predetermined frequency, all of the tuning capacitors are switched out of the resonant circuit except for the most significant capacitor, C<sub>1</sub>. The output voltage stabilisation device then acts to control the oscillator circuit so as to set the output amplitude to within a predetermined range of acceptable values. The voltage stabilisation is assumed to have occurred within a preset time period. At the end of the time period allowed for voltage stabilisation the determination of oscillator frequency is made. Voltage stabilisation may advantageously be inhibited during this period. Advantageously amplitude stabilisation is only performed after selection of a new capacitance value in the oscillator.

As part of the determination of the oscillator frequency a test is made to determine whether the oscillator frequency is higher than or lower than the target frequency. If the oscillator frequency is higher than the target frequency then the most significant capacitor is kept in the oscillator circuit, otherwise it is removed therefrom.

Following the setting of the most significant capacitor the process progresses to setting of the next most significant capacitor  $C_2$ . Once again the capacitor under test  $C_2$ , is switched into the oscillator circuit. The amplitude stabilisation device is then operated so as to control the oscillator output voltage to lie within a predetermined range of acceptable values, or to attain (within limits) a target value. Once the preset time period allocated to the amplitude stabilisation process has expired a test is then performed to see how the

----,--

oscillator frequency compares with the target frequency. If the frequency of the oscillator is higher than the target frequency then the capacitor  $\mathrm{C}_2$  is kept in the oscillator circuit, whereas if the oscillator frequency is lower than the target frequency the capacitor  $\mathrm{C}_2$  is removed.

3

The subsequent capacitors  $C_3$  to  $C_N$ , where  $C_N$  is the least significant bit, are then set in turn in accordance with the aforementioned procedure.

This "band switching" approach to control the oscillator enables the use of a reduced  $K_{\nu CO}$  in the oscillator and this 10 results in reduced phase noise.

Preferably the amplitude control is performed by controlling the bias current flowing from a current source/sink into or out of the oscillator circuit. Current flow control can be used to control the amplitude of the circuit since restricting 15 the current flow limits the rate of current change across inductors in the oscillator and hence the voltage developed across the inductors.

Preferably the frequency determination is performed by counting the voltage cycles from the oscillator and comparing the number of cycles with the output of a reference oscillator.

Preferably the amplitude control is performed digitally. The use of a digital amplitude control system results in non-obvious benefits in phase noise performance compared 25 to an analog feedback system. An analog system continually strives to adjust the oscillator amplitude towards a target value. This constant variation, and the devices used to achieve it, can give rise to additional phase noise.

By using a digital system, the individual voltage levels are 30 effectively invariant during the duration of each digital setting. This results in less noise being propagated into the oscillator and hence less phase noise at the output of the oscillator.

The oscillator performance in terms of actual oscillator 35 frequency for a given combination of capacitors switched into the resonant circuit or given response to a control voltage variation is not tightly specified. Neither is the oscillator amplitude. Provided that the oscillator's performance lies within a reasonable broad range of acceptable 40 values the PLL and the output voltage stabilisation device operate to effectively calibrate the oscillator performance. This in turn allows the use of simpler biasing schemes for the oscillator. It also removes the need to provide temperature compensation and reduces the need to design in supply 45 rejection. These attributes of the oscillator in turn allow the omission of circuit components, i.e., temperature compensation circuits, or the simplification of other associated circuits—i.e., power supply regulation. This in turn reduces the component count and hence the number of noise sources, 50 thereby reducing the introduction of noise into the oscillator and its control circuits/devices. This gives a reduction in

According to a second aspect of the present invention there is provided a method of controlling a voltage controlled oscillator having a tuneable output frequency and an adjustable output amplitude, wherein following a step of varying a tuning capacitor value, an amplitude control function is performed prior to making a determination of whether the oscillator is operating within an acceptable 60 frequency range.

According to a third aspect of the present invention there is provided an amplitude control system for a voltage controlled oscillator, wherein the control system is responsive to a measurement of oscillator amplitude and compares 65 this with a target amplitude to derive an amplitude error value, and wherein the error value is used to control a digital

amplitude controller such that changes in an oscillator amplitude control signal are quantised.

It is thus possible to provide an amplitude stabilisation system which does not adversely affect the phase noise performance of the oscillator.

Preferably the oscillator comprises a pair of matched transistors in a cross coupled configuration and connected to a current source (which term may also include a current sink). This configuration means that the current flowing in the oscillator is well defined and can be used to provide amplitude control of the oscillator.

Preferably the voltage developed across an inductor in a resonant circuit of the oscillator is monitored to provide a measurement of oscillator amplitude. The measurement of amplitude may be performed by rectifying the output of the oscillator and low pass filtering it to derive the measurement of the amplitude.

According to a fourth aspect of the present invention there is provided a method of controlling the amplitude of a voltage controlled oscillator having an amplitude control input, the method comprising the steps of determining an error between the oscillator amplitude and a target amplitude, and on the basis of the error measurement making a discrete adjustment to the amplitude control input, the amplitude control input being constrained to be one of a plurality of discrete values.

Advantageously the amplitude control is performed by a linear search, ramping up from the lowest amplitude value towards the target amplitude value. This approach, although slower than a successive approximation search, has the advantage that the maximum permissible oscillator amplitude is never exceeded. This is important as it can prevent the premature failure of devices within the integrated circuit due to excessive voltages occurring across them.

According to a fifth aspect of the present invention there is provided an apparatus for performing frequency compensation of the constant of proportionality of a voltage controlled oscillator within a phase locked loop, comprising a constant of proportionality modifier for modifying the constant of proportionality used in a frequency control loop as a function of a target frequency of the voltage controlled oscillator.

Preferably the frequency control is comprised of a coarse frequency control section and a fine frequency control section. The coarse frequency control section can be arranged to switch tuning capacitors in and out of a resonant circuit during a frequency space search in order to set the oscillator to approximately the correct frequency.

Once the coarse frequency adjustment has been performed, a fine frequency adjustment can be performed using a varactor (or equivalent component) to tweak the effective capacitance of the resonant circuit. Preferably the varactor is formed using one or more MOSFETs, where the gates are connected to the oscillator output and the sources and drains are connected to a frequency control port. The capacitance of the varactor will vary over one cycle, but the average capacitance is a function of the control voltage. This function contributes to the voltage-frequency gain of the oscillator ( $K_{VCO}$ ), which in turn contributes to the loop gain of the phase locked loop, which controls the varactor.

PLL loop gain affects bandwidth, lock time, phase noise and stability. This loop gain, and hence  $K_{{\cal V}CO}$ , should be well controlled if good response times are to be obtained, whilst avoiding feedback instability. Where MOSFET varactors are used,  $K_{{\cal V}CO}$  is a strong function of the oscillator amplitude and is therefore affected by frequency band, temperature, batch variations and frequency. Frequent amplitude calibra-

4

5

tions effectively remove the dependency of  $K_{PCO}$  on frequency band, temperature and batch-to-batch variations. Consequently we are left with an effective  $K_{PCO}$  that is simply a function of frequency. In fact the calibrated  $K_{PCO}$  is proportional to frequency³ or  $\omega$ ³. In a synthesizer PLL an output frequency or output signal is phase locked to a reference signal. A phase detector or phase frequency detector generates a negative feedback control signal which is proportional to the difference between the reference frequency  $F_{REF}$  and a feedback frequency where the feedback frequency  $F_{RE}$  is equal to the output frequency divided by  $F_{RE}$ , and  $F_{RE}$  is equal to  $F_{RE}$  is equal to  $F_{RE}$  and this is approximately equal to  $F_{RE}$ . In such a PLL the open loop again is proportional to  $F_{RE}$  divided by  $F_{RE}$  and this is approximately equal to

$$K_{VCO} \times \frac{F_{REF}}{F_{REF}}$$

i.e., the gain is proportional to

$$\frac{F^3}{F}$$

which is therefore proportional to F<sup>2</sup> where F is the output <sup>30</sup> frequency or carrier frequency.

According to a sixth aspect of the present invention there is provided a method of performing frequency compensation of the constant of proportionality of a voltage controlled oscillator, the method comprising forming a correction signal as a function of target frequency of the voltage controlled oscillator and applying the correction signal to a control input of the voltage controlled oscillator.

Preferably the correction signal varies, either smoothly or in a step wise fashion, as a function of frequency squared.

According to a seventh aspect of the present invention there is provided a voltage controlled oscillator for use in a telecommunications device, wherein amplitude and frequency control parameters of the voltage controlled oscillator are varied depending upon the mode of operation of the telecommunications device.

Thus in a GSM mode it may be desirable to run the local oscillator at increased amplitude during the transmit phase in order to maximise the signal to noise ratio within the transmitted signal, thereby reducing phase noise. However during receive a reduction in amplitude saves current and hence increases battery life. In a dual mode telephone, e.g., one supporting both GSM and a code division multiple access scheme then the oscillator amplitude may be reduced in CDMA transmission compared to that used for GSM transmission.

According to an eighth aspect of the present invention there is provided a controllable current source in combination with a voltage controlled oscillator, wherein the current source provides current to the oscillator for controlling the amplitude of oscillation thereof, and wherein the current source comprises a plurality of current mirrors arranged in parallel.

Preferably the current mirrors are weighted and digitally 65 controllable to switch them on or off. Advantageously the current mirrors are substantially binary weighted.

6

The use of the weighted current mirrors means that each mirror need only have a relatively low gain (for example unity) between its pair of transistors. Thus, any noise introduced into the side of the mirror defining the current is passed to the other side of the mirror without significant gain. Furthermore the noise from each of the individual mirrors is not coherent so the noise powers add as the square root of the sum of the squared contributions of the noise powers, whereas the currents add as a simple sum.

In the context of an oscillator control system where amplitude and frequency control is performed frequently it becomes possible to use circuit topologies that are simplified. The use of parallel current mirrors where the control current is defined by the current flowing through a resistor makes for a low noise mirror. The current mirror may receive its reference voltage from a regulator, such as a low drop out voltage regulator LDO. In this configuration current and voltage accuracy are not critical and hence the LDO and current mirror can be designed for low noise, even if this 20 is at the expense of a degradation in voltage regulation.

Thus, the decision to design a voltage regulator for low noise rather than for maximum regulation gives further noise improvements without comprising oscillator amplitude stability.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The present invention will further be described, by way of example, with reference to the accompany drawings, in which:

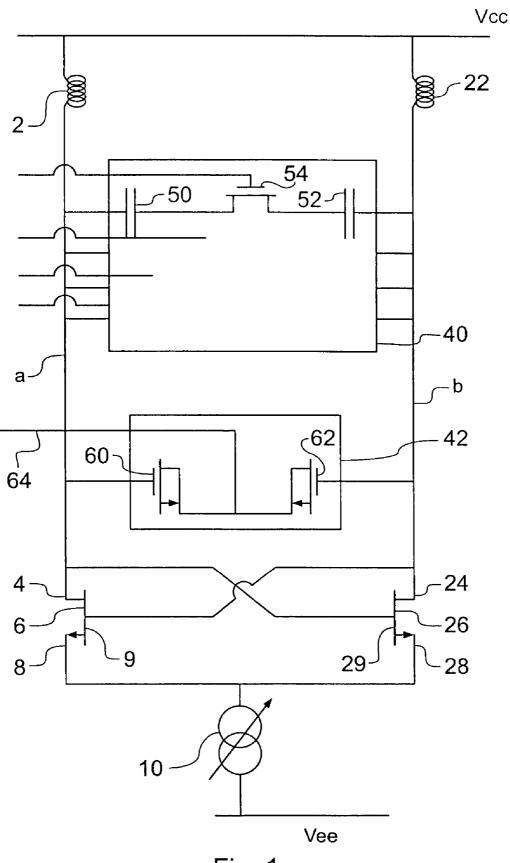

FIG. 1 schematically illustrates a voltage controlled oscillator:

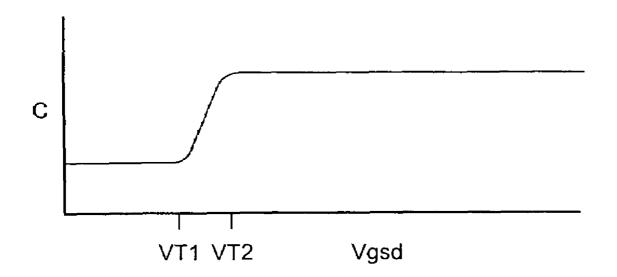

FIG. 2 schematically illustrates a capacitance exhibited by the varactor tuning elements of the oscillator shown in FIG. 1:

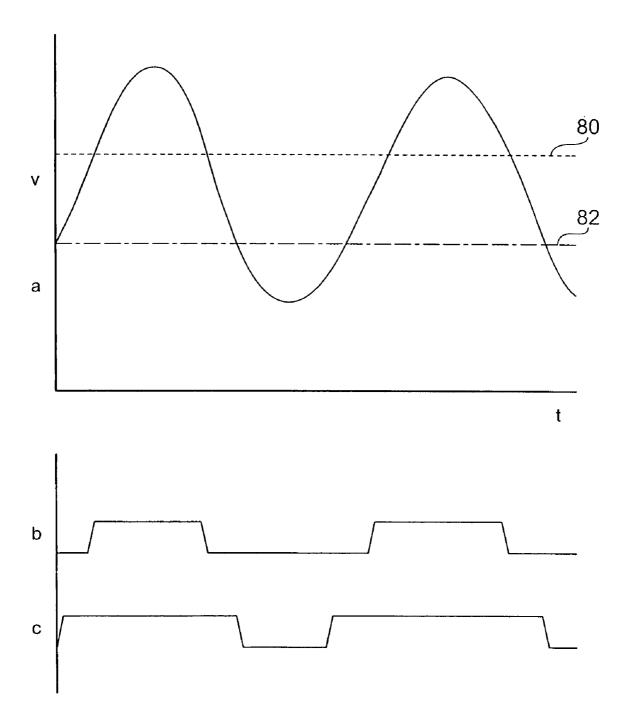

FIG. 3a schematically illustrates the peak to peak output voltage occurring at the input to one of the varactor elements compared to a switching voltage of the varactor, and FIGS. 3b and 3c illustrate the capacitance of the varactor over a cycle of operation of the oscillator for differing varactor control voltages.

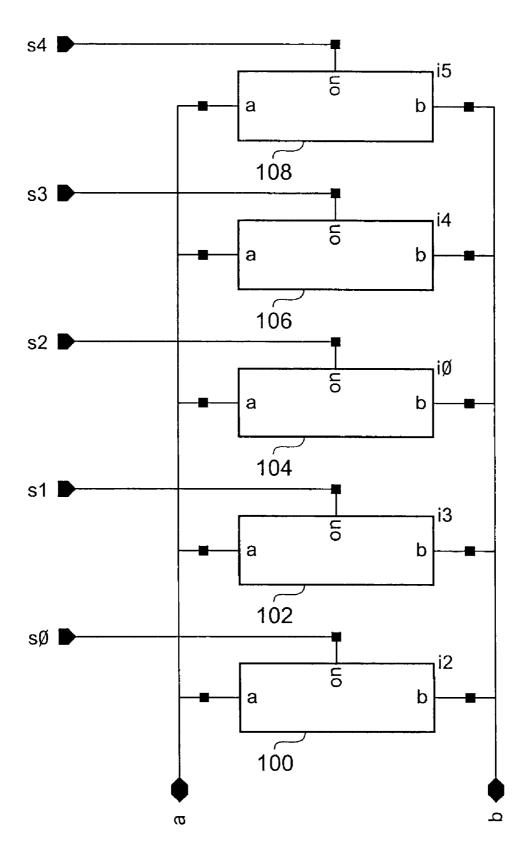

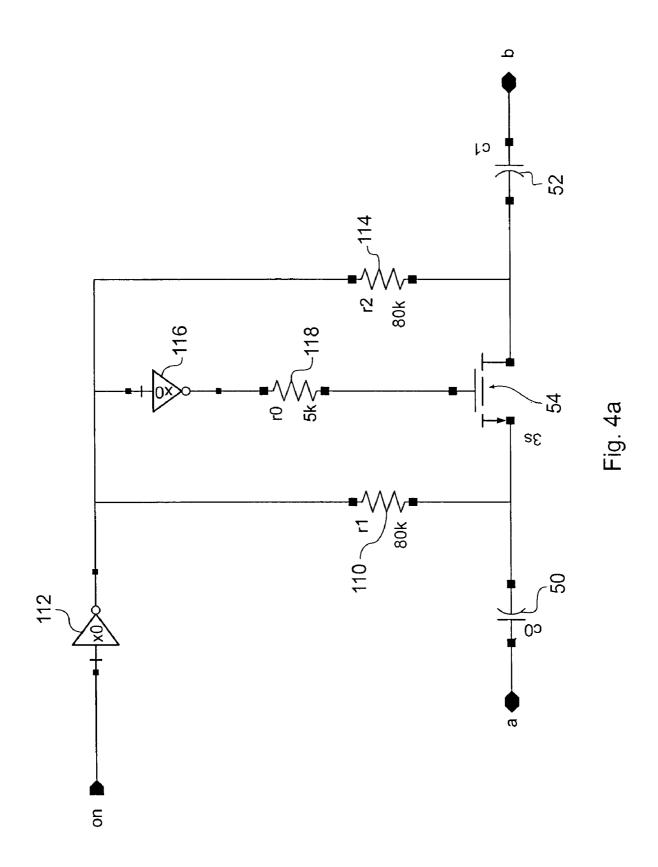

FIG. 4 schematically illustrates the configuration of the coarse tuning block of the oscillator of FIG. 1 and FIG. 4a shows the contents of a capacitor selection block in greater detail;

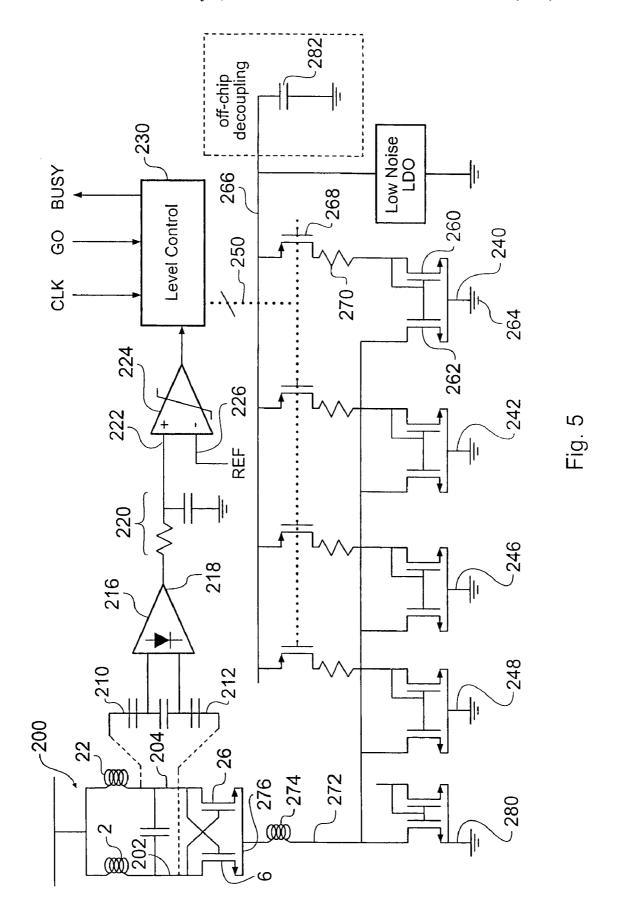

FIG. 5 schematically illustrates an oscillator output level control circuit;

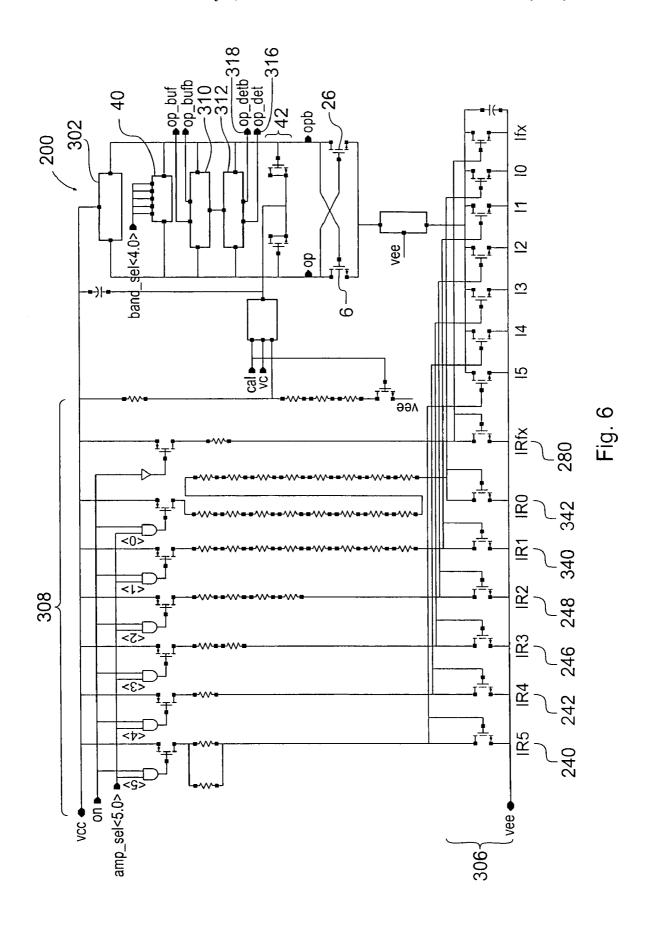

FIG. 6 is a circuit diagram of an embodiment of a level control circuit:

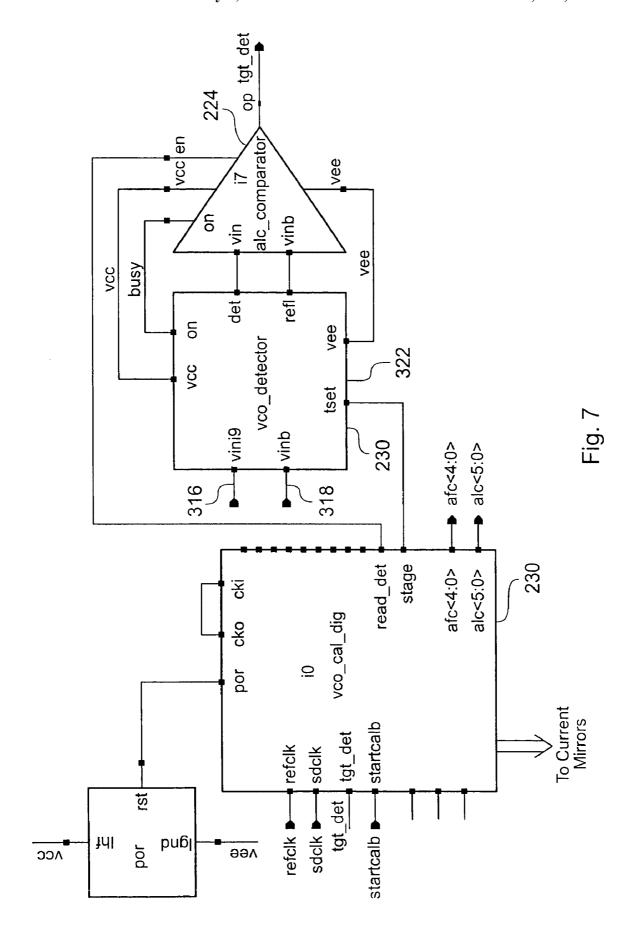

FIG. 7 is a circuit diagram of a level comparator in conjunction with its controller;

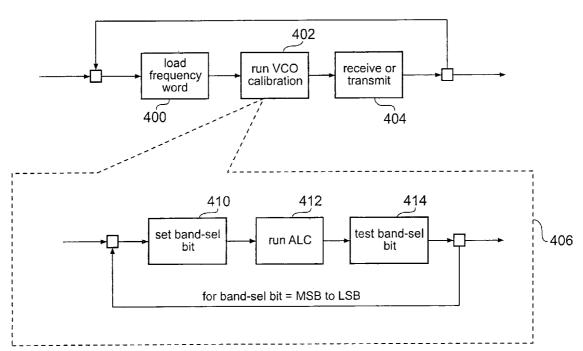

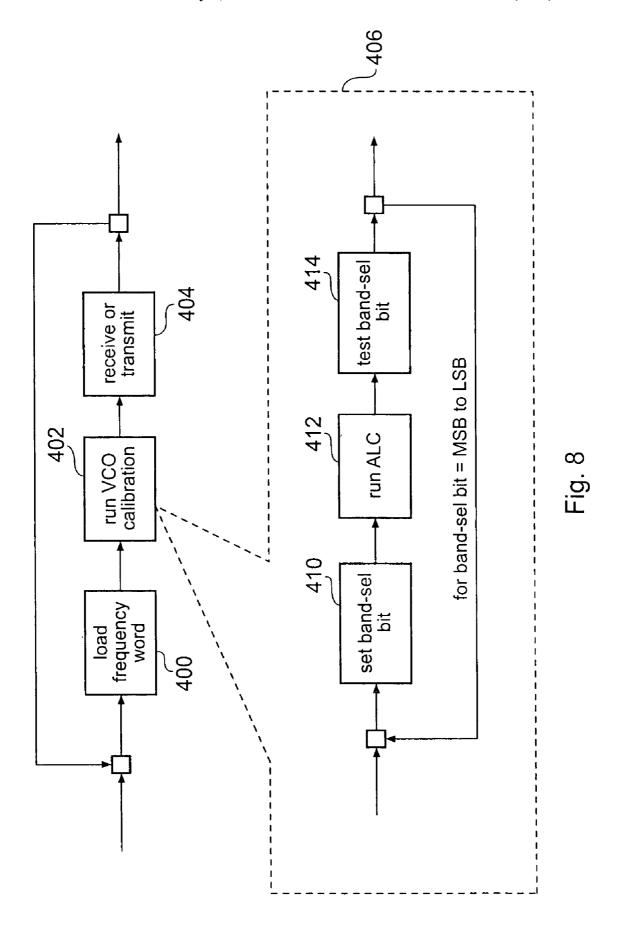

FIG. 8 is a flow diagram of a frequency control and amplitude control scheme;

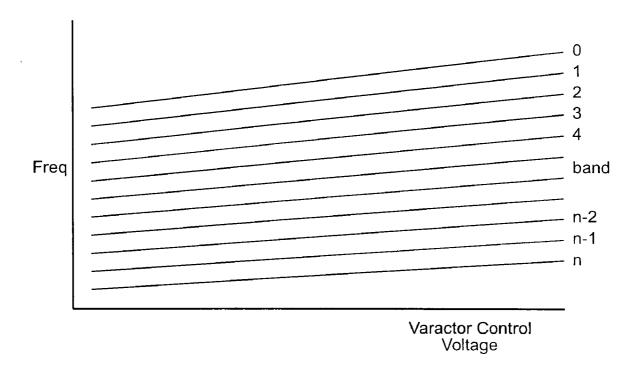

FIG. 9 is a diagram schematically illustrating the fre-55 quency range of the bands selectable by the VCO;

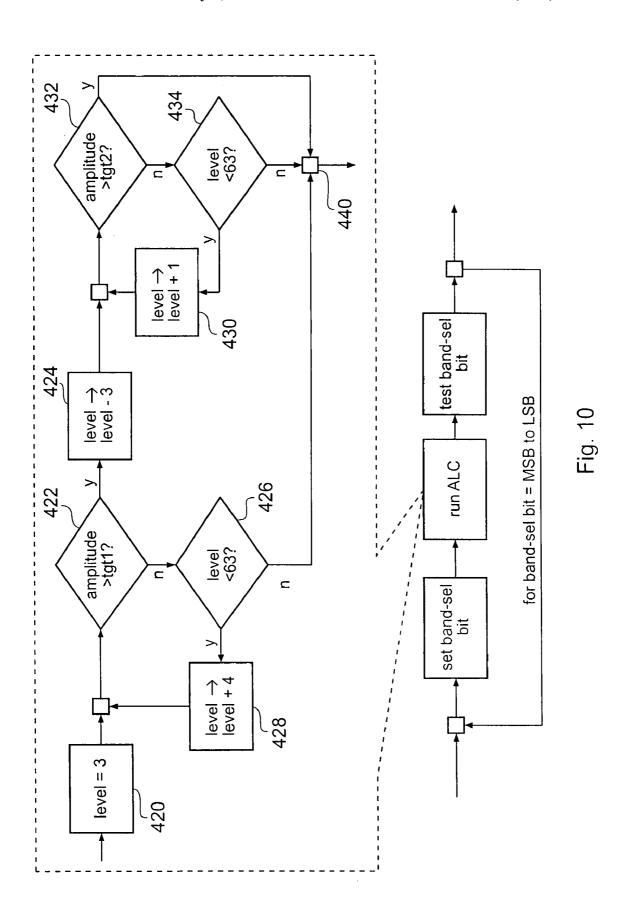

FIG. 10 shows part of the amplitude control scheme in greater detail;

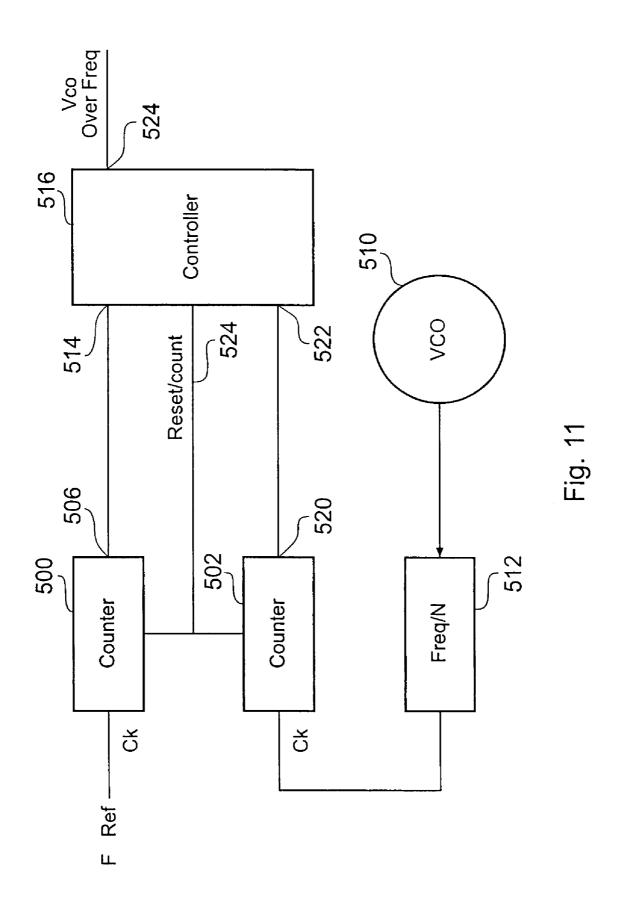

FIG. 11 schematically illustrates a circuit for comparing the oscillator frequency with a reference frequency; and

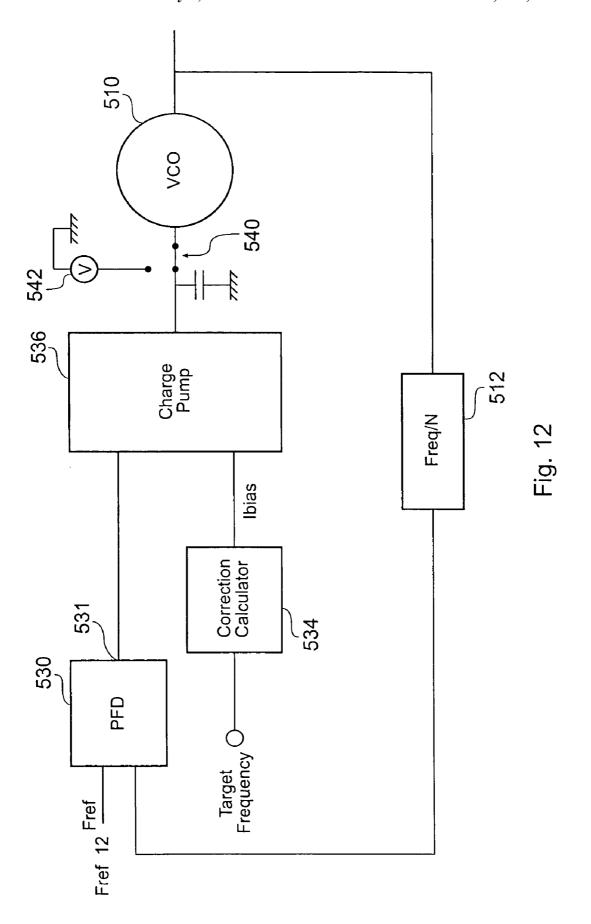

FIG. 12 schematically illustrates a circuit for performing fine frequency control of the oscillator.

FIG. 1 schematically illustrates an oscillator configuration which is suitable for use as a local oscillator and as a transmit oscillator in a mobile telephone. The oscillator comprises a first inductor 2 connected between a positive supply rail VCC and a drain terminal 4 of a first field effect transistor 6. A source 8 of the field effect transistor 6 is

connected to the output of a current control device such as a current source 10. Similarly a second inductor 22 is connected between the supply rail VCC and a drain 24 of a second field effect transistor 26. A source 28 of the second field effect transistor 26 is also connected to the output of the 5 current source 10. The field effect transistors 6 and 26 are cross coupled such that a gate 9 of the first field effect transistor 6 is connected to the drain 24 of the second field effect transistor 26, and a gate 29 of the second field effect transistor 26 is connected to the drain 24 of the first field 10 effect transistor 6. Finally, a variable capacitance is provided between the drain of the first field effect transistor 6 and the drain 24 of the second field effect transistor 26. The capacitance is provided via a digitally controlled bank of capacitors 40 which gives coarse frequency control of the voltage 15 control oscillator and via a varactor unit 42 which provides fine frequency control of the VCO output frequency.

The capacitor selection unit comprises a plurality of capacitors which can be switched into or out of the circuit between the drains 4 and 24 of the field effect transistors. For simplicity only one of the electronically controllable capacitors within the capacitor bank 40 is schematically illustrated in FIG. 1. It can be seen that each one of the electronically controllable capacitors actually comprises two capacitors 50 and 52 disposed either side of a field effect transistor 54. The 25 transistor 54 can be switched on to switch the capacitors into the oscillator circuit, or switched off thereby effectively removing the capacitors from the oscillator circuit, apart for the residual parasitic capacitance that they have. The values of the capacitors within the channels of the switchable 30 capacitance block 40 are advantageously binary weighted so as to simplify control of the tuning range.

The specific details of the capacitor selection unit are shown in more detail in FIG. 4. As shown in FIG. 4, the capacitor tuning block 40 comprises five binary weighted 35 capacitor blocks 100, 102, 104, 106 and 108 arranged in parallel. Each capacitor block has its own select signal S0 to S4 which controls whether the capacitor within the respective block is switched into or removed from the circuit formed between the connections A and B in FIG. 4, which 40 connect to nodes formed between the inductor 2 and transistor 4 on the one hand, and the node formed between the inductor 22 and the transistor 24 on the other hand in FIG. 1. Within each block a field effect transistor and capacitor are connected in series between the nodes A and B of the 45 resonant circuit. Transistor acts merely as a switch in that it is driven to be either in a high impedance or a low impedance state in response to a control signal.

FIG. 4a illustrates the internal configuration of one of the capacitor blocks in greater detail. As described earlier a 50 capacitor 50, a field effect transistor 54 and a further capacitor 52 are connected in series between the nodes "A" and "B". However in order to ensure consistent operation of the circuit both the source and drain of the field effect transistor 54 are connected via resistors 110 and 114 to the 55 output of an inverter 112 which receives a "capacitor select" signal at its input. The output of the inverter 112 is also provided as an input to a further inverter 116 whose output is connected to a gate of the transistor 54 via a resistor 118. The circuit causes the transistor 54 to be switched hard on 60 thereby minimising the on resistance for a given device size, whilst also allowing the device to be switched hard off, small devices are advantageous as they have reduced parasitic capacitance. Furthermore the circuit is completely balanced.

Returning to FIG. 1, the varactor 42 is of a known design 65 and comprises two field effect transistors 60 and 62. A gate of the transistor 60 is connected to the drain 4 of the first

8

field effect transistor 6 whereas a gate of the transistor 62 is connected to the drain 24 of the second field effect transistor 26. The drains and sources of the transistors 60 and 62 are connected together and also to a varactor control line 64. The voltage between the gate and the drain and source of each of the transistors 60 and 62 can be considered as effectively changing the dimensions between the insulated gate and the conducting channel (which is effectively one of the plates of the capacitor) within each of the transistors 60 and 62 thereby giving rise to the variation of the capacitance exhibited by the varactor 42.

Ideally the change of capacitance of the varactor with respect to a control voltage on the control line 64 would be linear. FIG. 2 schematically illustrates the response of the varactor. In FIG. 2 the abcissa represents the control voltage applied to the varactor which is the voltage between the gate and the source/drain of each of the transistors 60 and 62 (the sources and drains being coupled together). The ordinate of FIG. 2 represents the capacitance of the varactor. It can be seen that as the control voltage rises from zero towards a first threshold VT1 the capacitance of the varactor remains essentially unchanged. The capacitance then rises steeply as the control voltage rises from VT1 towards VT2. For control voltages above VT2 the capacitance increases only very slowly with increasing control voltage. The voltages VT1 and VT2 are relatively close together and hence the varactor response can be considered as having an essentially digital response with a short transition region in the range VT1 to VT2.

FIG. 3a schematically illustrates the voltage occurring at the drain of one of the transistors 6 and 26 with respect to time. Also schematically illustrated on FIG. 3a are two voltages 80 and 82 which represent differing control voltages applied on the varactor control line 64. However it will be appreciated that the varactor does not in fact respond solely to the voltage on its control line 64 but in fact responds to the voltage difference between the voltage on the control line 64 and the voltage at the gates of the transistors 60 and 62. Consequentially the varactor responds to the sum of the alternating voltage and the DC control voltage. Consequently, over an operating cycle of the voltage controlled oscillator, the varactor can be turned on and off, as shown in FIG. 3b and FIG. 3c with the mark-space ratio between the on periods and the off periods being varied by changing the DC control voltage on the input line 64. FIG. 3b shows the consequence of having a relatively low control voltage on the control line 64 such that the sum of the control voltage and the output voltage from the oscillator only exceeds the switching threshold for a relatively short period of time, that is when the voltage across the varactor's transistor exceeds the threshold represented by the chain line 80. FIG. 3c shows the effect of having a larger DC input voltage on the control line 64 such that the varactor switching voltage is exceeded when the output of the oscillator exceeds the threshold indicated by the chain line 82. Thus in FIG. 3c the varactor spends longer in its higher capacitance regime than is the case in FIG. 3b. This means that, averaged out, the varactor in the FIG. 3c regime has a higher capacitance than that in the FIG. 3b regime and consequently the oscillating frequency of the voltage controlled oscillator will be reduced compared to the FIG. 3b regime.

As noted hereinbefore, gross frequency selection is determined by selecting or deselecting the various capacitors within the capacitor bank 40. The selection and deselection of such capacitors results in changes in the components contributing to the oscillator circuit, and this invariably leads to changes in the quality factor, Q, of the oscillator.

This in part can be visualised as resistive losses within the switching transistor **54**. These changes in quality factor give rise to changes in the amplitude of the oscillator output. Changes in the amplitude of the oscillator output give rise to variations in the time for which the voltage VGSD across the 5 varactor exceeds the switching threshold and hence it becomes apparent that the frequency of the voltage controlled oscillator is dependant upon the amplitude of the output of the voltage controlled oscillator.

Consequently, in order to obtain good frequency control  $^{10}$  it is necessary for the amplitude of the voltage control oscillator to be stabilised. It should be noted that changes in output amplitude of the VCO effectively change the proportionality constant  $K_{VCO}$  of the oscillator and this in turn varies the loop gain of a phase locked loop, PLL, used to  $^{15}$  control the operating frequency of the VCO.

There are two operating regimes of the circuit shown in FIG. 1 which give rise to control or limitation of the amplitude of the voltage oscillations, and hence the output, of the VCO. The first limiting regime is a current limiting 20 regime. The voltage across each of the inductors 2 and 22 is given by

$$V = L \frac{di}{dt}$$

Where

$\frac{di}{dt}$

is the rate of change of current through the inductor.

Given that the oscillator has a nominal switching frequency it follows that the rate of change of current

$\frac{di}{dt}$

limited by the bias current supplied from the current source  $_{45}$  10. Thus the voltage waveform developed across the inductors 2 and 22 can be controlled by varying the current flowing through the current source 10.

An alternative limiting regime is a voltage control regime which occurs because the current source 10 will, in reality, 50 be built using transistors and these will require a minimum voltage head room across them in order to operate properly. Consequently, as the amplitude of oscillation increases the voltage head room across the current source 10 decreases. Eventually the head room across the current source 10 decreases to such an extent that it ceases to function correctly. This necessarily results in limitation of the voltage control oscillator output voltage.

Both of these amplitude limiting processes are analog processes and essentially unpredictable. It therefore 60 becomes necessary to control the current mirror by way of a feedback circuit.

It might be supposed that this would best be done in the analog domain. Thus the peak to peak amplitude of the oscillation within the voltage control oscillator would be 65 measured using a peak to peak detector and this voltage would be supplied to a first input of an error amplifier. The

10

second input of the error amplifier would receive a reference voltage and the output of the error amplifier would be a function of a difference between the measured peak to peak voltage and the target peak to peak voltage. The output of the error amplifier is then provided to a control input of the variable current source 10 so as to stabilise the amplitude of oscillation of the VCO.

Whilst this technique is satisfactory from the point of view of amplitude control, it is unsatisfactory with regard to the noise performance of the voltage control oscillator. The very fact that the feedback is continually trying to stabilise the output voltage introduces noise into the circuit by way of the current source. Noise in the current source results in noise in the amplitude of oscillation of the oscillator. Noise in the amplitude of oscillation is, by virtue of the process schematically illustrated in FIGS. 3a to 3c converted to noise in the phase domain of the VCO. This noise degrades phase performance of the VCO and may in fact preclude the device from meeting the stringent phase noise requirements laid down in the GSM specification. Similar oscillator performance requirements are found in other telecommunication systems.

The inventors have realised that, in order to obtain an acceptable phase noise performance from a circuit shown in 25 FIG. 1, analog control of the current source in order to control oscillator amplitude is undesirable.

The inventors have realised that digital control of the current source provides enhanced phase noise performance. This is because the periodic nature of digital control means that for the majority of the time that the current source is running, the current control signal to the current source is invariant. The unchanging nature of the current control signal means that the control signal does not become a source of noise in the current supplied by the current source and consequently does not get converted to phase noise by virtue of the action of the VCO. Within a time domain multiplexed system the changes in the bias current may be constrained to occur when the telephone is not engaged in transmitting and/or receiving.

Within a CDMA system such constraints are not so easily achieved, in which case the size of change of oscillator bias current should be constrained so as not to cause the received or transmitted symbols to become corrupted.

FIG. 5 schematically shows an oscillator and level control circuit (which forms part of an oscillator controller) constituting an embodiment of the present invention. The oscillator, generally indicated 200, is of the type described hereinbefore with reference to FIGS. 1 to 4. Connections are made to nodes 202 and 204 representing the connection between inductor 2 and transistor 6 in a first side of the oscillator 200 and between inductor 22 and transistor 26 in a second side of the oscillator 200, respectively. The connections from nodes 202 and 204 extend, via decoupling capacitors 210 and 212 to first and second inputs of a rectifier 216 which rectifies the voltage difference to obtain a measure of the peak to peak amplitude of the output of the oscillator. An output 218 of the rectifier 216 is supplied via a low pass filter 220 to a non-inverting input 222 of a comparator 224. An inverting input 226 of the comparator 224 receives a reference input indicative of the target amplitude of the oscillator 200. An output of the comparator is provided to a level controller 230 which provides control signals to a plurality of digitally controllable current mirrors 240, 242, 244, 246 and 248 via a control bus 250. It will be appreciated that more current mirrors can be provided if desired. The current mirrors have a common structure and, for brevity, only the first current mirror 240 will be described

in detail. The mirror 240 comprises a pair of matched transistors 260 and 262 whose gates are coupled together. The transistors 260 and 262 also have their source terminals coupled together and to the local ground connection 264. The drain terminal of the transistor 260 is connected to a 5 supply rail 266 via an electrically controlled switch 268 and a current control resistor 270. The drain terminal of transistor 262 is connected to the oscillator 200, and more particularly to a node 272 at an input of an inductor 274 which in turn connects to a node 276 to which the sources of the 10 transistors 6 and 26 are connected. The inductor 274 is beneficial as it presents a high impedance to oscillations propagating into the current mirror. Other current control configurations are possible, such as merely switching resistors into the path between the oscillator and ground, or 15 switching resistors into and out of the reference arm of the current mirror 240. The biasing scheme is simple in that it does not include temperature compensation and has low supply rejection.

As noted hereinbefore, all of the current mirrors have the same configuration, but the values of the current control resistors vary between the mirrors. The current mirrors are advantageously binary weighted. If mirror **240** is the most significant mirror, then if the resistor **270** in the mirror **240** has a value R, then the current control resistor in the next mirror has a value 2R, such that half the current flows in mirror **242** compared to that flowing in current mirror **240**. The value of the current control resistor in the current mirror **246** is 4R, the value of the current control resistor in the next current mirror **248** is 8R, and so on.

A further current mirror 280 is provided whose current is the minimum amount required to sustain operation of the oscillator (plus a margin of safety) and this current mirror 280 is permanently on.

The supply rail 266 could be derived from a voltage reference, but advantageously is the voltage supply rail to the oscillator core 200. In this way, decoupling capacitor 282 plays a dual role, ensuring stability and limiting noise bandwidth at the LDO output (a function which is usually essential) and simultaneously limiting noise bandwidth in the bias generation circuits.

For simplicity the supply to the oscillator core may be via a low drop out voltage regulator (i.e., a regulator which does not require much voltage headroom) which may be of a 45 relatively simple design. The regulator is advantageously not designed to maximise regulation but instead is designed to minimise noise. This improves phase noise performance of the oscillator.

FIGS. 6 and 7 show an embodiment of an oscillator in 50 accordance with the present invention and as schematically shown in FIG. 5. The oscillator, generally labelled 200 corresponds functionally with the circuit shown in FIG. 1. The inductors 2 and 22 are implemented within functional block 302, coarse tuning is implemented by the switchable 55 capacitors within the tuning block 40 and fine control is performed by the varactor 42. The cross coupled field effect transistors 6 and 26 receive current from a current mirror generally designated 306. The various transistors within the current mirror 306 are controlled by a switching circuit 308. 60 Returning to the oscillator 200, it further includes a buffer circuit 310 which makes a buffered version of the output of the oscillator available for use in other parts of the telecommunication device. Also provided is a detection tap circuit 312 which provides signals 316 and 318 representing the 65 amplitude of oscillation. The outputs of the detector tap circuit 312 are provided to a further detection element 322,

12

shown in FIG. 7, which serves to rectify and smooth the signals on lines 316 and 318 to produce a composite detected signal

The detection element 322 also receives a target amplitude from a controller 230 via input 330. The detection element compares the prevailing amplitude with the target value and outputs the result of the comparison to the non-inverting input of a comparator 224. The inverse of the comparison is provided to the inverting input of the comparator 224. The comparator 224 acts to scale and level shift the output of the detection element 320 such that a digital signal suitable for use by other digital circuits is obtained.

The controller 230 (FIG. 7) can control the amplitude of the oscillator by virtue of the current mirror 10 (FIG. 1). The current mirror (shown in detail in FIG. 6) comprises six digitally controllable binary weighted current mirrors 240, 242, 246, 248, 340, 342, together with one permanently on channel 280 which ensures that a minimum value current flow always exists. This is useful as it prevents the oscillator being turned off inadvertently.

The GSM telephone mobile system is a time division multiple access, TDMA, system in which the mobile telephone only transmits or receives during predefined slots. Thus it becomes possible to perform digital control of the oscillator amplitude during the periods where the telephone is not transmitting or receiving and then to suspend amplitude control, that is effectively to go "open loop" during the transmit or receive burst in the TDMA system. However the present invention can also be applied to code division multiple access, CDMA, systems, including 3G telephone systems, where the transmitters and receivers are continuously active. The application of the present invention to CDMA systems is appropriate because the periodic nature of digital systems means that the control word or signal to the current source, i.e., current mirror 10 is still only periodically updated and hence during the majority of a clock cycle the control signal/word is invariant and hence not a source

Although the oscillator voltage can vary with temperature and supply voltage it is a reasonable expectation that these vary relatively slowly. Thus amplitude correction need only be performed periodically. In fact, the amplitude correction could be performed once and only once at power up. However, for improved performance it would be expected that it would be repeated every now and again in order to account for temperature changes, for example because heat from the user's hand causes gradual warming of a mobile telephone

The mobile telephone may have to be frequency agile. For example the GSM telephone system may require the mobile telephone to change operating frequency during the telephone call. If the frequency change is instructed the telephone only has a period of about 200 µs to set its operating frequency before its next transmit cycle.

Manufacturing tolerances and dependence on temperature means that the oscillator configuration shown in FIG. 1, when implanted within a integrated circuit is not wholly predictable. Therefore when selecting a transmission frequency a frequency search through the oscillator frequency space is performed in order to determine the most appropriate selection of capacitors within the coarse tuning unit 40 to be switched into, and indeed out of the oscillator.

Given that the capacitor values within the selection block 40 are binary weighted, the capacitors are switched in and out of the oscillator circuit to perform a successive approximation search of the frequency space. In such a search the most significant, that is largest, capacitor is switched into the

circuit and the measurement of the oscillation frequency is made to determine whether the oscillator is higher or lower than the target frequency. If the oscillator is higher than the target frequency then the capacitor remains selected, otherwise it is switched back out of the oscillator circuit. Then the 5 next most significant capacitor is switched into the oscillator circuit and again a frequency measurement is made to determine whether the oscillator frequency is higher or lower than the target frequency. If the oscillator is higher than the target frequency then the capacitor remains 10 selected, otherwise it is removed from the circuit again. This process is repeated for each of the capacitors, it being borne in mind that the selection of each capacitor reduces the operating frequency.

Due to the interrelation of the amplitude and oscillating 15 frequency, the inventors have realised that it is appropriate to interleave amplitude stabilisation with the capacitor frequency search. This is achieved by integrating the tests such that once the first capacitor is switched into the circuit, an amplitude test and stabilisation is performed prior to making 20 the frequency measurements and frequency decision. Indeed, the process can be extended such that once the first capacitor is selected, selection or initiation of the second capacitor test causes the amplitude control to be performed again before the frequency measurement step associated 25 with the second capacitor is performed. The process can also be repeated in respect of the third and subsequent capacitors although it could reasonably be expected that as the capacitor selection moves from the most significant to the least significant capacitor, amplitude variation associated with 30 this process will also reduce. Thus the designer has an option to inhibit the amplitude stabilisation for the least significant capacitors if so desired.

FIG. 8 is a block diagram schematically illustrating the frequency or band selection and level control procedure as 35 implemented within a mobile telephone constituting an embodiment of the present invention. A controller (not shown) handles the processing of control signals with the mobile telephone infrastructure. Thus, before commencing the procedure shown in FIG. 9 the controller has already 40 received and decoded instructions concerning what frequencies the telephone is to receive and transmit on.

The procedure commences at step **400** where a new frequency word is loaded. This word represents the target frequency of the voltage controlled oscillator. Control then 45 passes to step **402** where the VCO calibration is performed. Once this has been completed control is passed to step **404** where, a transmit or receive operation is performed. From step **404** control can pass to other procedures (not shown) or can be directed by the controller to return to step **400**.

Step 402 is in fact an iterative step which itself causes several steps to be performed. Sub-steps to step 402 are schematically illustrated within the outlined box 406 in FIG. 8. The VCO calibration involves a successive approximation search through frequency space to lock the oscillator to a 55 frequency band which includes the desired frequency.

As described hereinbefore, the coarse tuning of the oscillator is controlled by the switching of binary weighted capacitors (although binary weighting is not essential). Fine control can be performed using the varactor. During the 60 frequency selection the varactor is set to its minimum capacitance value. This has the consequence that the varactor can only be used to fine tune the oscillator's frequency is a downwards direction. Other modes are possible, for example the varactor could be set to its maximum capacitance and hence fine frequency control would be in the direction of increasing frequency.

14

FIG. 9 shows how the operating frequency varies with the capacitance control word and varactor voltage. Thus if the capacitance control word is set to 0 corresponding to its minimum value and with all capacitors nominally switched out of the oscillator, then the oscillator will oscillate at its highest frequency. As the control word is increased sequentially towards its maximum value N, then the 1 st, 2nd . . . to Nth bands are selected, each having a lower initial frequency than the preceding band. It is important for frequency coverage that the bands overlap with at least the nearest adjacent band so as to ensure that there are no gaps in the operating range between the minimum and maximum frequencies that have to be produced.

Suppose that there are 64 tuning bands, labelled 0 to 63, available. Those can be selected via a 6 bit control word. If we assume that the least significant bit is bit 0, and the most significant bit is bit 5, then the VCO set up procedure performs the frequency search as follows.

The frequency select bits are successively tested from bit 5 to bit 0 by repeatedly running steps 410, 412 and 414 (FIG. 8)

Thus, at step 410 the bit under test of the frequency control word is set. During the first pass through this test this is bit 5. Control is then passed to step 412 where amplitude level control is performed. Once the oscillator amplitude has been set control is passed to step 414 where is a comparison of the oscillator frequency is made with the target frequency as defined by the frequency control word which was loaded at step 400. The comparison is made by measuring the oscillator against a reference frequency provided from a crystal oscillator.

If the oscillator is running at a higher frequency than the target, then the control bit is kept, otherwise it is reset.

The next most significant bit is selected and steps 410, 412 and 414 are repeated. Thus after 6 passes through this process the correct frequency band has been located. Advantageously, if the last frequency control bit (LSB) is not kept, a further amplitude level control cycle might be run to adjust amplitude for the actual band which has been selected.

Oscillator control is then passed to the phase locked loop which locks on to the target frequency and makes fine adjustments of the oscillator frequency via the varactor control voltage.

FIG. 10 schematically illustrates the processes performed within step 412 of FIG. 9.

Although a successive approximation search through the amplitude space would be quick, it runs the possibility that the maximum permissible amplitude might be exceeded, and possibly by a large margin. This might be damaging to the components within the oscillator. A slower but safer strategy is to perform a linear search starting from the lowest amplitude and ramping up towards the target amplitude. However, better still is a linear search involving both coarse steps and fine steps of amplitude adjustment. This is both safe and fast. The algorithm schematically illustrated in FIG. 10 performs such a search. The current provided by the current source is controlled by an amplitude control word which has been designated "level". The value of "level" is constrained to lie between zero and 63.

There are two target values TGT1 and TGT2, which are employed during the coarse and fine phases of the search respectively. The value of TGT1 is constrained to be less the maximum safe amplitude minus the maximum expected coarse step size. TGT2 is set equal to the value of the required amplitude minus the equivalent of ½ of the least significant bit.

The algorithm commences at step 420 where "level" is set to an initial value of three. Control is then passed to step 422 where a comparison of the oscillator amplitude is made with a first target value TGT1. A comparison is made at step 422, and if the value of the oscillator amplitude exceeds the first target TGT1, then control is passed to step 424. However, if the value of the oscillator amplitude is still less than TGT1 control passes to step 426 where a test is made on the value of "level". If the value of "level" is less than 63 control is passed to step 428 where the value of "level" is increased by four and control is then returned to step 422. However if the test at step 426 determines that the value of "level" is not less than 63, control is then passed to step 440 which represents an exit from the amplitude control routine.

If step 422 passes control to step 424, then step 424 acts to decrement the value of "level" by three. Control is then passed to step 432 where the oscillator amplitude is compared with the second target, TGT2. The value of the second target TGT2 is set to the required amplitude of the oscillator minus one half the value of the least significant bit of the level control. If step 432 determines that the amplitude is greater than the value TGT2 then control is passed to step 440 which represents the exit from the level setting routine. However if step 432 determines that the oscillator amplitude is less than TGT2 then control is passed to step 434. Step 434 tests the value of "level" and if it is less than 63 then control is passed to step 430, otherwise control is passed to step 440. At step 430 the value of "level" is incremented by one. Control is then passed to step 432.

FIGS. 11 and 12 schematically illustrate circuits which are suitable for determining the frequency of oscillation of the oscillator shown in FIG. 1. As noted hereinbefore the telephone can be instructed to set its oscillator to any one of a predetermined series of frequencies. The frequencies are 35 not randomly chosen, but in fact are pre-allocated channel frequencies. Each GSM telephone is provided with a highly accurate oscillator which forms a frequency and timing reference for the telephone.

In the circuit shown in FIG. 11 the oscillator controller comprises two counters 500 and 502 which are of an identical construction. The first counter 500 receives the frequency reference signal Fref at a clock input and divides the frequency signal by a predetermined number, for 45 example 32. At the end of this division an output 506 of the counter 500 will change state, for example by going to a logical high. The counter 502 is connected to the voltage controlled oscillator 510 via a fractional divider 512. As noted hereinbefore the target VCO frequency is a multiple of the frequency reference. This multiple of the frequency reference is designated N. Thus, if the fractional divider 512 is programmed to divide by N then the signal provided to the second counter 512 should be at the same frequency as that 55 circuit. provided to the first counter 500. Consequently a comparison of the VCO frequency with the target frequency can be performed merely by starting both counters 500 and 502 at the same time, getting them to count the same number of clock pulses, and determining which finishes first. The one that finishes first will be clocked at a higher rate, subject to a small quantization error resulting from the fact that we cannot guarantee that both clocks to counters 500 and 502were in phase at the start of the count. The output 506 of the 65 first counter 500 is provided to a first input 514 of a controller 516. An output 520 of the second counter 502 is

16

provided to a second input 522 of the controller 516. The controller 516 can reset the counters 500 and 502, or allow them to start counting via a shared control line 524. Thus, the reset/control line 524 may go low to reset the counters, and may be sent high to initiate the count. If the signal is received from the counter 502 before the counter 500 then an output 524 asserting that the voltage control oscillator is running faster than the reference can be asserted.

It is thus possible to provide a relatively simple and reliable circuit configuration for setting the coarse frequency of the voltage controlled oscillator.

FIG. 12 shows the circuit configuration for performing the fine frequency control of the voltage controlled oscillator 510. Here, as in FIG. 12, the output of the VCO is divided down by the fractional divider 512. A phase-frequency sensitive detector 530 is provided which receives the frequency reference signal at a first input thereof and the output of the fractional divider 512 at a second input thereof. The phase-frequency sensitive detector, which is a well known component, produces an output 531 representative of the phase difference between its input signals. This signal, whose polarity and magnitude represents the correction to be applied to the voltage controlled oscillator, is supplied to a first input of a charge pump 536. A correction calculator 534 is responsive to a frequency control word from the controller and outputs a correction value to a second input controlling a bias current of the charge pump 536. The output of the charge pump is low pass filtered and used to control the varactor 42 in the voltage controlled oscillator 510.

The correction calculator **534** can advantageously be implemented as a lookup table as this allows the degree of resolution and the shape of the function that the correction calculator implements to be varied at the designer's will. In general, the correction calculator will implement a function that varies as frequency squared in order to compensate for the fact that the change in frequency with respect to the change in capacitance varies as the frequency cubed.

Given that the coarse frequency control and fine frequency control are performed in independent control loops it is desirable to be able to inhibit operation of the fine frequency control loop during the coarse frequency control. In order to achieve this a switch **540** is provided at the input to the VCO. The switch can be selected so as to connect the input of the voltage controlled oscillator to a reference voltage **542** in order to maintain the varactor frequency control at a predetermined value.

It is thus possible to provide a voltage controlled oscillator which has low phase noise, and which is relatively inexpensive by virtue of being integrated into an integrated circuit.

The invention claimed is:

- 1. A variable frequency oscillator comprising:

- a variable frequency oscillator core comprising a plurality of capacitors selectively connectable to a resonant circuit so as to control a frequency of the oscillator; an oscillator controller; and

- an output voltage amplitude stabilization device for maintaining an amplitude of an oscillator output within a predetermined range, wherein the variable frequency oscillator core is controllable to operate in one of a plurality of frequency bands and has a frequency control input responsive to the oscillator controller, and

- where in order to set a new operating frequency the oscillator controller performs a frequency search to set the output frequency of the oscillator by:

- a) making an adjustment to the frequency of the oscillator by connecting or disconnecting a capacitor from the 5 resonant circuit of the oscillator;

- b) adjusting an amplitude of oscillation of the oscillator to attain a target value prior to testing the output frequency of the oscillator to compare it to a target frequency;

- c) comparing the oscillator frequency with a target frequency; and d) on the basis of the comparison repeating steps a) to c) until an appropriate selection of capacitors to be connected to the resonant circuit has been made.

- 2. A variable frequency oscillator as claimed in claim 1, 15 in which the frequency search is a successive approximation search.

- 3. A variable frequency oscillator as claimed in claim 1, in which the oscillator is in series with a current control device and the magnitude of the current through the current 20 control device can be varied in order to control the amplitude of the output signal of the oscillator, and wherein the current control device is digitally controlled.

- 4. A variable frequency oscillator as claimed in claim 3, wherein the current control device comprises a plurality of 25 resistors arranged in parallel, each resistor having an electrically controllable switching device associated with It such that current flow through each resistor can be selectively enabled or inhibited.

- 5. A variable frequency oscillator as claimed in claim 3, in which the current control device comprises a plurality of current sources connected in parallel, and the current sources are individually controllable to switch them on or off.

- 6. A variable frequency oscillator as claimed in claim 5, in which the current sources are binary weighted.

- 7. A variable frequency oscillator as claimed in claim 3, in which the oscillator controller is responsive to a measurement of amplitude of the oscillator, and the oscillator controller adjusts the current in the current control device so as to maintain the amplitude of the oscillator in an acceptable range.

- 8. A variable frequency oscillator as claimed in claim 7, in which the oscillator controller selects the current to flow in the oscillator on the basis of a substantially monotonically increasing current until the correct amplitude is reached.

- 9. A variable frequency oscillator as claimed in claim 1, in which the oscillator is a voltage controlled oscillator and the oscillator frequency is controlled by a phase locked loop, and wherein a correction factor varying as a function of  $_{50}$ frequency is applied to the voltage controlled oscillator.

- 10. A variable frequency oscillator as claimed in claim 1, in which amplitude stabilization is performed only during tuning of the oscillator via band selection.

- 11. A mobile telephone including a voltage controlled 55 oscillator as claimed in claim 1.

- 12. A variable frequency oscillator comprising:

- a variable frequency oscillator core;

- an oscillator controller; and

- an output voltage amplitude stabilization device for main- 60 taining an amplitude of an oscillator output within a predetermined range,

- wherein the variable frequency oscillator core is controllable to operate in one of a plurality of frequency bands and has a frequency control input responsive to the 65 oscillator controller, and where in order to set a new operating frequency the oscillator controller performs a

18

- frequency search through the bands to identify an appropriate band and wherein:

- a) amplitude stabilization is performed during the frequency search through the bands, such that following selection of a frequency band the output voltage stabilization device is operated to control the amplitude of the oscillator to attain a target amplitude prior to testing the operating frequency of the oscillator;

- b) the oscillator is in series with a current control device and the magnitude of the current through the current control device can be varied in order to control the amplitude of the output signal of the oscillator, and wherein the current control device is digitally controlled;

- c) the oscillator controller is responsive to a measurement of amplitude of the oscillator, and the oscillator controller adjusts the current in the current control device so as to maintain the amplitude of the oscillator in an acceptable range;

- d) the oscillator controller selects the current to flow in the oscillator on the basis of a substantially monotonically increasing current until the correct amplitude is reached; and

- e)the oscillator controller performs a coarse search of the current required to reach an acceptable amplitude, and then refines this with a fine search so as to refine the current supplied so as to control the amplitude of the oscillator.

- 13. A variable frequency oscillator in which a current in the oscillator controlling the magnitude of oscillation is monotonically increased in steps of a first size until such time as a first target oscillation amplitude is exceeded, in which after the first target oscillation amplitude is exceeded the amplitude is successively increased in steps of a second step size less than the first step size until such time as the amplitude exceeds a second target amplitude.

- 14. A variable frequency oscillator as claimed in claim 13, in which once the first target oscillation amplitude is exceeded the current is decremented.

- 15. A variable frequency oscillator as claimed in claim 14, in which the current is decremented by at least the first step

- 16. A method of setting a frequency of a oscillator having a plurality of capacitors selectively connectable to a resonant circuit of the oscillator to control a frequency of the oscillator and also having an amplitude control, the method comprising performing a frequency search to set the output frequency of the oscillator by repeating the steps of:

- a. making an adjustment to the frequency of the oscillator by connecting or disconnecting a capacitor from the resonant circuit of the oscillator;

- b. adjusting an amplitude of oscillation of the oscillator to attain a target value prior to testing the output frequency of the oscillator to compare it to a target frequency;

- c. comparing the oscillator frequency with a target frequency; and

- d. on the basis of the comparison repeating steps a to c until an appropriate selection of capacitors to be connected to the resonant circuit has been made.

- 17. A method as claimed in claim 16, in which the amplitude of oscillation is adjusted using a search procedure in which an adjustment is made to an amplitude control parameter, and the resultant amplitude is measured and a further adjustment of the amplitude control parameter is made if the amplitude has not attained the target amplitude.

- 18. A method as claimed in claim 16, in which the amplitude control parameter is increased from a minimum value towards a maximum value until the target amplitude is achieved.

- 19. A method as claimed in claim 18, in which a coarse 5 setting procedure is used to find an approximate amplitude by incrementing the amplitude control parameter using a first step size, and once the value has been approximated a fine setting procedure is implemented in which the changes of a second step size, smaller than the first step size, are 10 made to achieve the target amplitude.

- 20. A method as claimed in claim 16, in which the oscillator amplitude is controlled by virtue of the current supplied to the oscillator and the current is controlled in a digital manner to control the amplitude of the oscillator.

- 21. A method as claimed in claim 20, in which the current is supplied by a plurality of electronically controllable current sources, and the current sources are binary weighted, and selected ones of the current sources are switched on to achieve a desired current.

- 22. An amplitude control system for an oscillator, wherein the control system is responsive to measurement of oscillator amplitude and compares this with a target amplitude to derive an amplitude error value, and wherein the amplitude error value is used to control a digital amplitude controller 25 such that changes in an oscillator amplitude control signal are quantized, wherein the amplitude error value is merely indicative of whether the oscillator amplitude is one of greater than and less than the target amplitude, the control system successively increments the oscillator amplitude 30 from a minimum value to the target value and during a first

20

phase of amplitude control the amplitude control signal is incremented in steps of a first step size until a first acceptable approximation to the target amplitude is achieved, and thereafter a second phase is implemented in which adjustments of a second step size are made to achieve a second acceptable approximation to the target value, the second step size being smaller than the first step size.

- 23. An amplitude control system as claimed in claim 22, in which the first acceptable approximation of the target amplitude is smaller than the second acceptable approximation of the target amplitude.

- 24. An amplitude control system as claimed in claim 22, in which once the first acceptable approximation is exceeded, the amplitude control signal is decremented by the first step size before proceeding to the second phase.

- 25. An amplitude control system as claimed in claim 22, wherein the amplitude control signal is used to drive a digitally controlled current supply device.

- 26. An amplitude control system as claimed in claim 25, wherein the digitally controlled current supply device comprises a plurality of current mirrors arranged in parallel, the current mirrors being individually controllable between being on and off.

- 27. An amplitude control system as claimed in claim 26, wherein the current mirrors are binary weighted.

- 28. An amplitude control system as claimed in claim 25, wherein the digitally controlled current supply device comprises at least one current mirror which is permanently on.

\* \* \* \* \*